SDSoC设计开发流程 软件设计与开发详解

SDSoC(Software-Defined System-on-Chip)是由赛灵思(Xilinx)提供的一种高层次综合(HLS)开发环境,专门用于在Zynq SoC或FPGA平台上加速软件应用。典型的SDSoC设计开发包括多个步骤,其中软件设计与开发是核心环节,对整个系统性能和效率具有决定性影响。以下是典型的SDSoC设计开发中的软件设计与开发步骤概述。

第一步:需求分析与算法设计

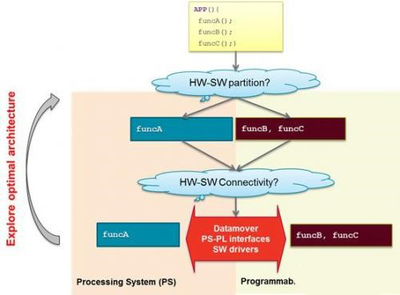

在软件设计与开发之初,需要明确应用需求,例如计算密集型任务(如图像处理、机器学习推理)的加速目标。开发者分析软件算法的可并行性和数据流,识别适合硬件加速的函数或循环部分。通常,这涉及将C/C++代码划分为软件部分(运行在处理器上)和硬件加速部分(运行在FPGA逻辑上)。

第二步:编写C/C++代码

开发者使用标准C/C++语言编写应用代码,无需直接处理硬件描述语言(如VHDL或Verilog)。代码应遵循SDSoC兼容的规范,例如避免使用动态内存分配或复杂的指针操作,以确保后续综合的可行性。关键函数可添加pragma指令(如#pragma SDS)来指定数据传输和内存管理。

第三步:软件仿真与验证

在SDSoC环境中,首先进行软件仿真,验证C/C++代码的功能正确性。开发者可以使用标准调试工具(如GDB)或SDSoC内置的仿真器,模拟硬件加速部分的行为。这一步有助于识别逻辑错误和性能瓶颈,确保算法在软件层面正确运行。

第四步:硬件加速函数标记与优化

使用SDSoC工具,开发者标记需要硬件加速的函数,并通过HLS优化参数(如流水线、数据流)来提升性能。这包括配置数据传输方式(例如,使用AXI总线进行DMA传输),并优化内存访问模式以减少延迟。SDSoC会自动生成硬件IP核和必要的接口逻辑。

第五步:系统构建与综合

在SDSoC IDE中,执行系统构建过程,将软件代码与硬件加速部分集成。工具会调用Vivado HLS和Vivado设计套件,将C/C++函数综合为硬件逻辑,并生成完整的比特流文件和软件可执行文件。开发者需配置平台设置(如目标设备型号和时钟频率),并处理可能的时序约束。

第六步:硬件仿真与协同验证

构建完成后,进行硬件仿真或使用硬件平台(如Zynq评估板)进行验证。SDSoC支持协同仿真,允许软件在处理器上运行,同时与FPGA硬件交互。开发者通过性能分析工具(如SDSoC性能分析器)监控加速效果,检查吞吐量、延迟和资源利用率,并根据结果优化代码。

第七步:部署与测试

将生成的比特流和可执行文件部署到目标硬件上,进行实际测试。这包括运行完整应用,验证功能正确性和性能提升,并可能进行迭代优化。SDSoC提供的运行时库(如SDS库)简化了软件与硬件的通信,确保高效执行。

SDSoC的软件设计与开发流程从算法分析到部署,强调高层次抽象,使软件工程师能够高效利用FPGA加速,而无需深入了解硬件细节。通过这种方法,可以显著缩短开发周期,并实现性能与能效的平衡。

如若转载,请注明出处:http://www.ncf88888.com/product/14.html

更新时间:2026-01-15 10:33:11